# **PLDWorld.com**

2001 10 4 / Version 2.0...

```

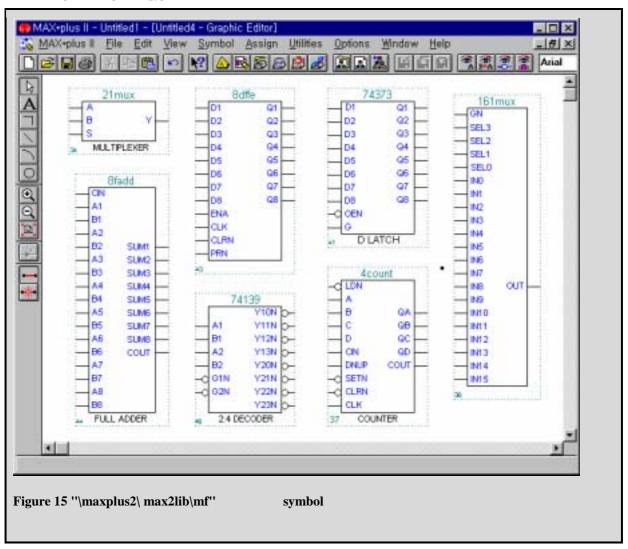

, Schematic Capture

... MAX+plus II

, IC

... CPLD FPGA

(Logic) ...

ALTERA PLD FLEX10K Series EPF10K10QC208-4

...

MAX+plus II Project , Schematic

Design Compilation, Simulation ...

```

...

1

MAX+plus II

MAX+plus II

Directory Folder MAX+plus II Directory

『C:』 D:』가

©C:\max2work\exp\_a©D:\max2work\exp\_aDirectory©L:\max2work\exp\_aDirectoryDirectory

"4-Bit Binary Up/Down Counter with Synchronous Load (LDN), Asynchronous Clear, and Asynchronous Load (SETN)"

8-Bit Binary Counter

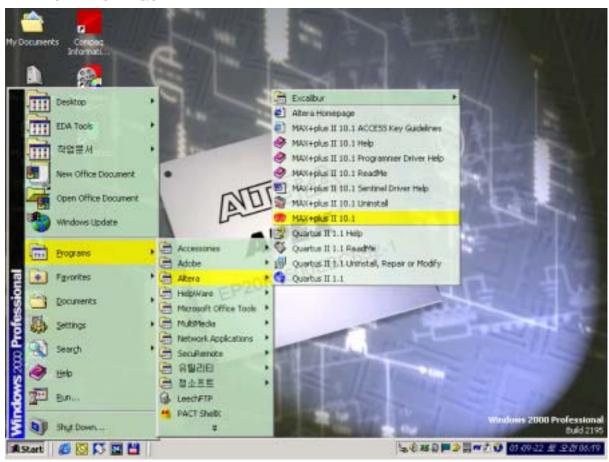

PC MAX+plusII 10.1 1 Windows 95/98/NT/2000 -> **(P)** -> **Altera** -> **MAX+plus II 10.1** MAX+plus II .

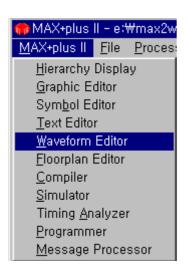

Figure 1 MAX+plus II

MAX+plus II 2

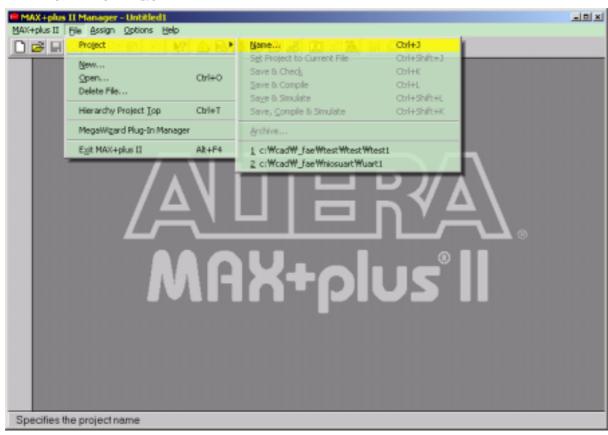

. Project 2

"Untitled1" .

Figure 2 MAX+plus

Toolbar MAX+plus II

Toolbar .

Figure 3 MAX+plus II Toolbar

2

# Graphic Design File

| 2  | (Schema                | atic Capture)  |       |       |           |

|----|------------------------|----------------|-------|-------|-----------|

|    | Project                | Graphic Editor |       |       |           |

|    |                        |                |       |       |           |

| 1. | (Proje                 | ct name) .     |       |       |           |

| 2. | (New file              |                |       |       |           |

| 3. | Sch                    | nematic        |       | •     |           |

| 4. | Logic                  | (Symbol) .     |       |       |           |

| 5. | Symbol                 |                |       |       |           |

| 6. | (input pin)            | (output pin)   | •     |       |           |

| 7. | Node Bus               |                |       |       |           |

| 8. | Pin                    | •              |       |       |           |

| 9. | •                      |                |       |       |           |

| 10 | .Target Device         | •              |       |       |           |

| 11 | .File Co<br>Rule Check | ompiler<br>.)  | Error | Check | . (Desigr |

| 12 | .File Close .          |                |       |       |           |

|    |                        |                |       |       |           |

|    | Proje                  | ct .           | •     |       | 4         |

|    |                        |                |       |       |           |

PLDWorld.com

## Figure 4 Project

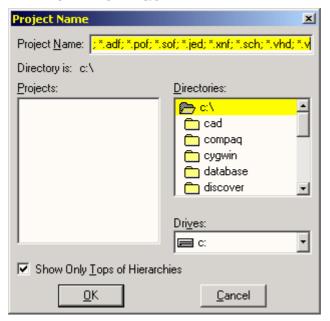

4 Name... Project 5 Project .

Figure 5 Project

"Drives:" "Directories:"

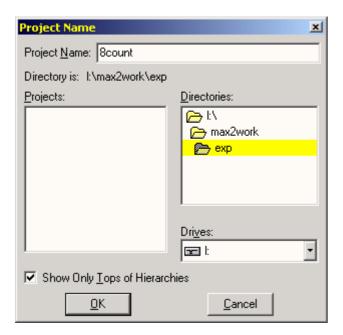

(L:\max2work\exp) . "Project  $\underline{N}$ ame:"

Project 8counter .

Figure 6 Project (8count)

OK 7 Project .

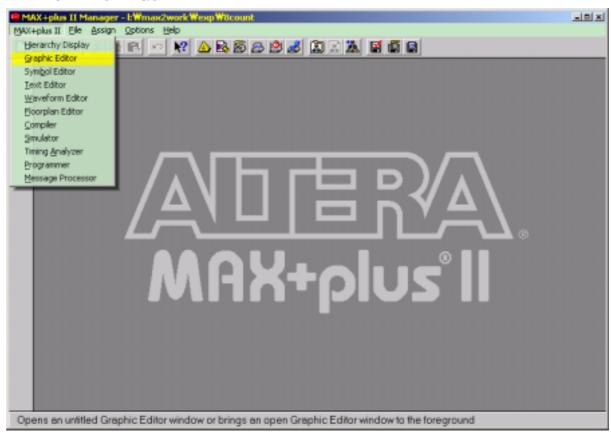

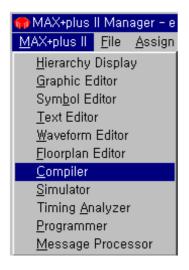

Figure 7 [MAX+plus II] Submenu [Graphic Editor]

Schematic File .

7 MAX+plus II Submenu <u>G</u>raphic Editor 8

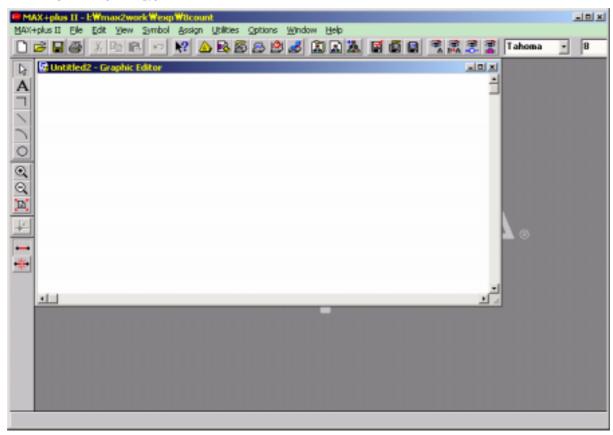

## Figure 8 Graphic Editor

Graphic Editor 가 Menu [File] [Save As....] .

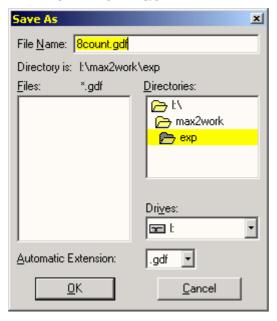

Figure 9 GDF File

Project , gdf 8count.gdf OK 10 가 Graphic Editor

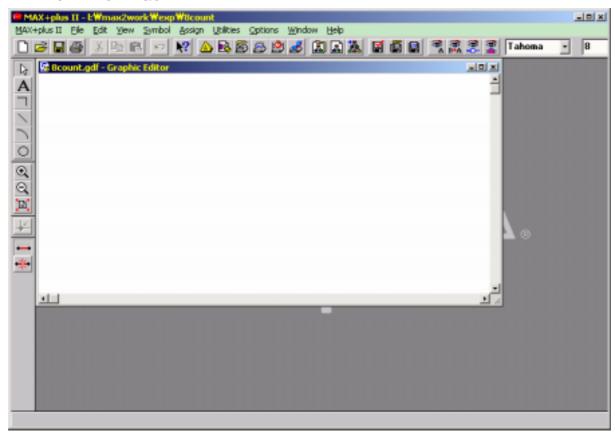

Figure 10 8count.gdf Schematic

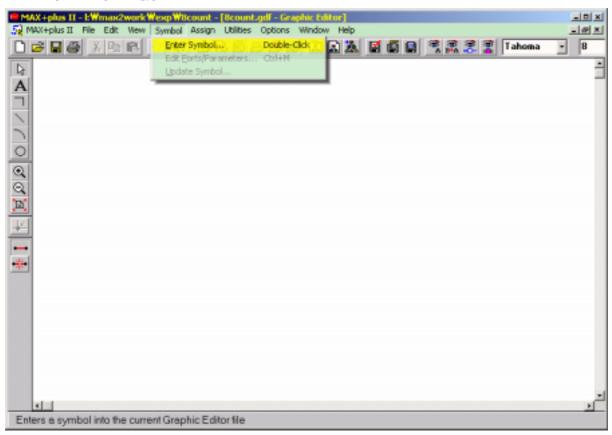

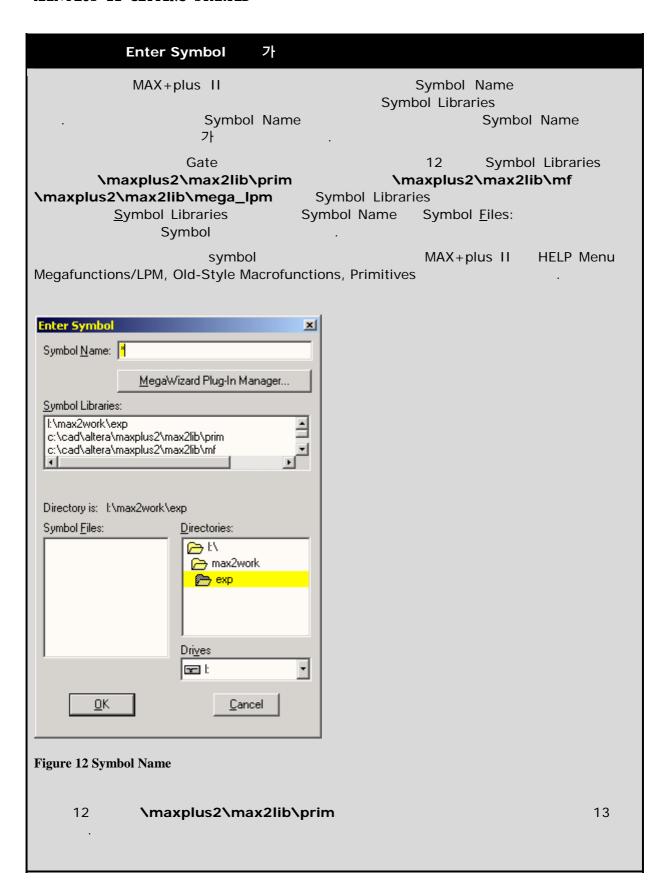

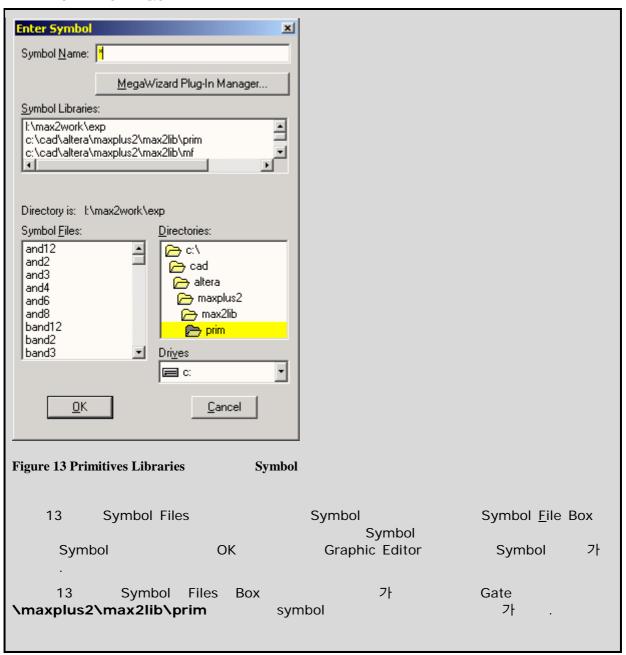

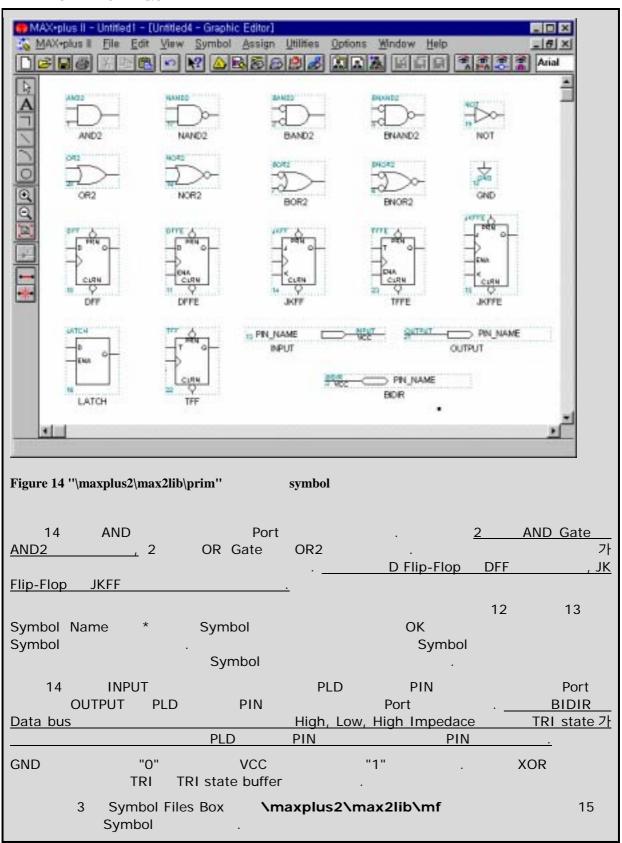

| Graphic Editor<br>가  | Symbol<br>Graphic | Editor   |        |             | 11     | •                |

|----------------------|-------------------|----------|--------|-------------|--------|------------------|

| [Symbol]             |                   |          | Symbol | Double-Clid | ck]    | , <u>Graphic</u> |

| Editor               |                   |          |        |             |        |                  |

|                      |                   | <u>.</u> |        |             |        |                  |

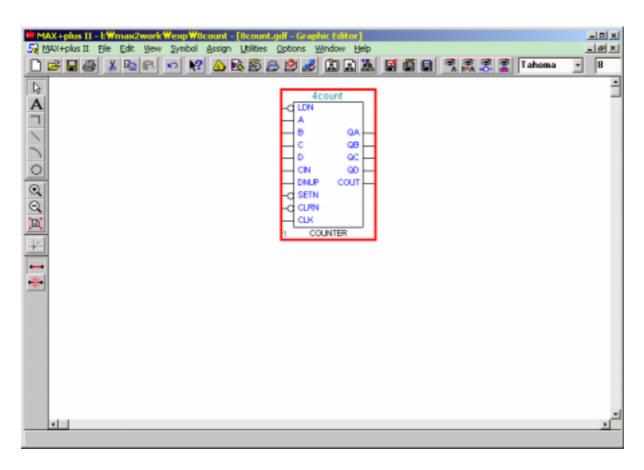

| 4-Bit Binary Up/Down | Counter           |          | Sym    | bol Name    | 4count | Enter            |

| Key OK               |                   | •        | J      |             |        |                  |

Figure 11 [Symbol] [Enter Symbol... Double-Click]

Symbol Name 4count OK 16

Figure 16 4count

|      | 4count   |       |               |          |  |

|------|----------|-------|---------------|----------|--|

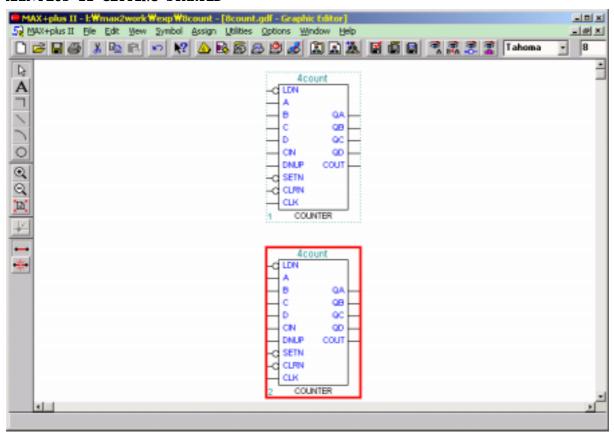

| Сору | 가        |       |               |          |  |

|      |          | Paste | 가 ,           | 4count 가 |  |

| ·    |          |       |               |          |  |

|      | Ctrl Key |       | 4count Symbol | 1        |  |

| Drag |          |       |               | . ( 가    |  |

|      | .)       |       |               |          |  |

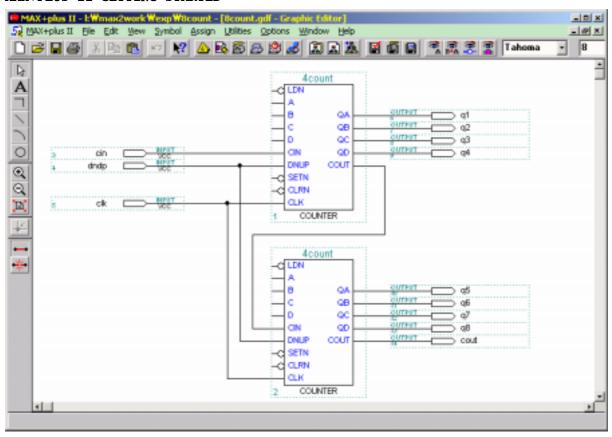

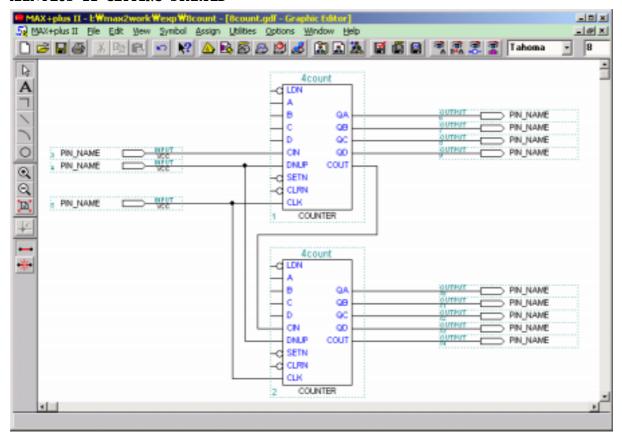

Figure 17 4count

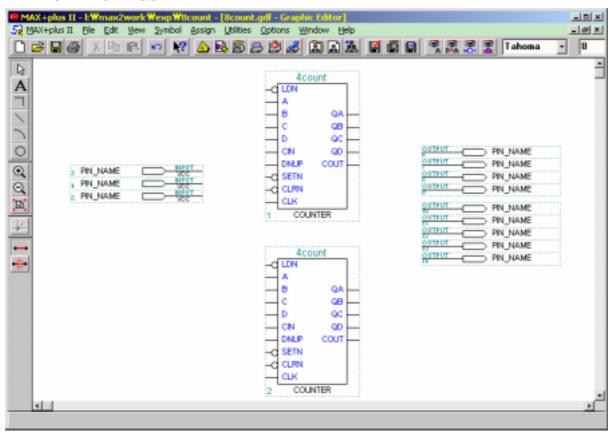

input 3 output 9 . 18

PLDWorld.com

Figure 18 Line 8count

- . 🔍

- . <u>Q</u>.

- 🖺 -

- (Connection dot)

- Symbol (Rubberbanding function on)

- Symbol (Rubberbanding function off)

Figure 19 Graphic Editor

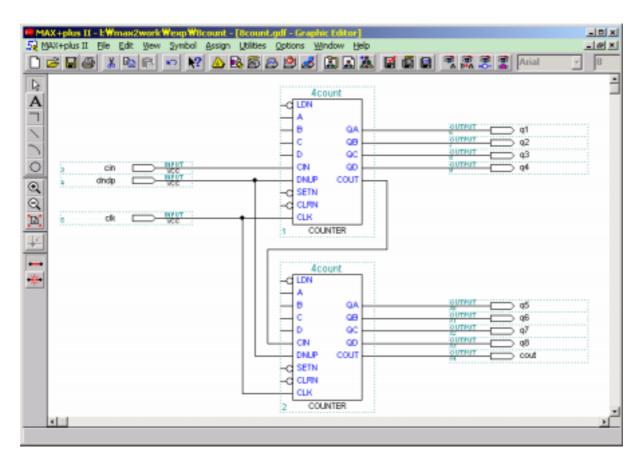

19 INPUT PORT OUTPUT PORT

Port PIN\_NAME

Button PIN\_NAME

cin, dndp, clk q1, q2, q3, q4, q5, q6, q7, q8, cout

Pin 20 .

Figure 20 Pin Name

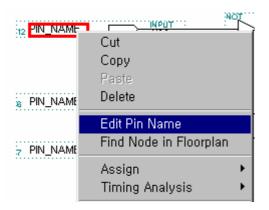

PIN\_NAME

20 Edit Pin Name PIN\_NAME 7

Pin Name .

PIN\_NAME 21 .

Figure 21 Pin Name

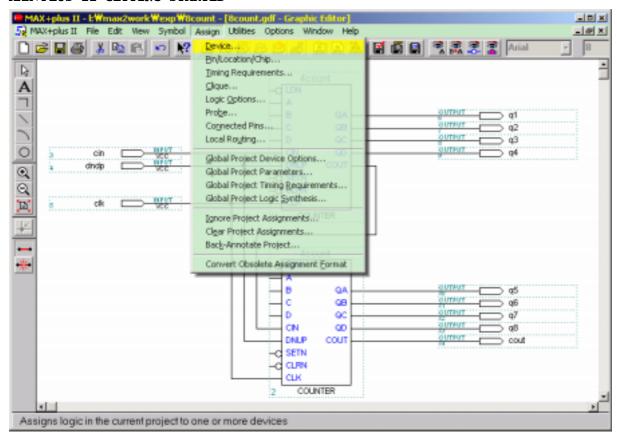

Figure 22 PLD DEVICE

Device Device Family 가 AUTO

22 Assign Device 23 Device

FLEX10K Series EPF10K10QC208-4 OK

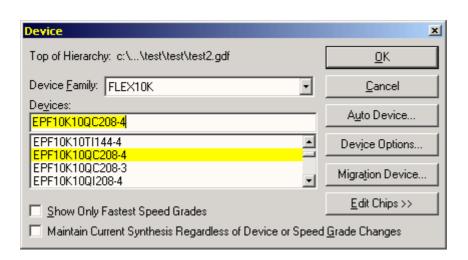

Figure 23 DEVICE

, 23 EPF10KQC208-4

EPF10KQC208-3 24 Fastest Speed

Grades .

## ✓ Show Only Fastest Speed Grades

Figure 24 7 Device Option

| 2<br>EPF10KQC208-4 가               |                | Only Fastest Sper<br>F10KQC208-4 | ed G | <b>rades</b> " Disable<br>OK . |

|------------------------------------|----------------|----------------------------------|------|--------------------------------|

| FLEX10K<br>EPF10K10QC208-4<br>Chip | 10 Series<br>가 | EPF10K10QC208-3<br>가             | 가    | Speed 가<br>Performance         |

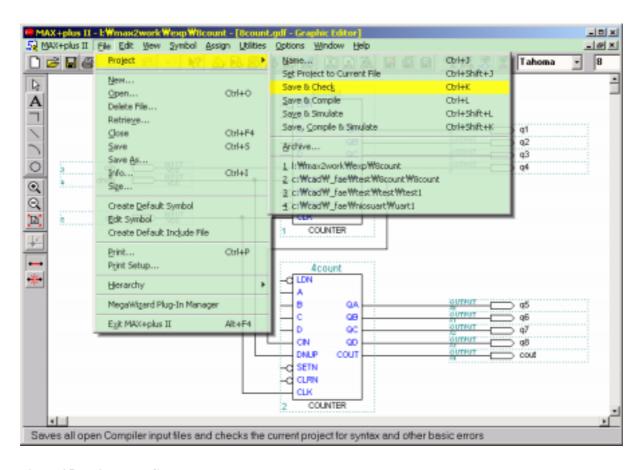

| . 25                               | Schematic      |                                  |      | Design Rule Check              |

Figure 25 Design Rule Check

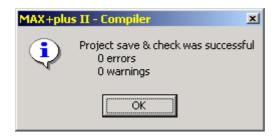

File -> Project -> Save & Check

Figure 26 Design Rule Check

Figure 27 Design Rule Check 가

Graphic Editor

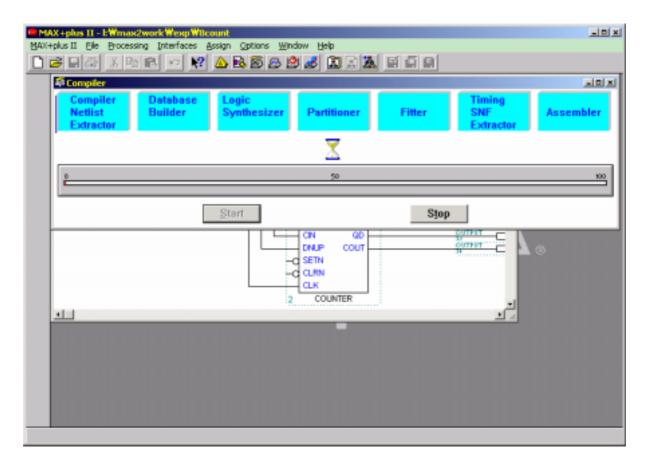

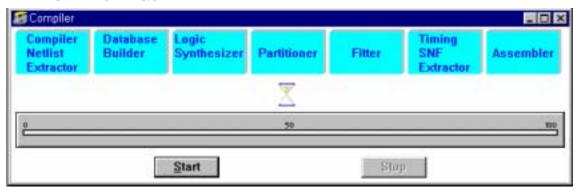

Figure 28 Compiler

MAX+plus II (Module) Utility

Project (Error) Logic Synthesize Project

ALTERA Chip Fitting

Project Design File File

Compiler 29

Figure 29 Compiler

30 .

Figure 30 Compiler

Figure 31 Compile

(warning) (error)가 ALTERA Help 가 31 Design Rule Check 가 Compile Timing SNF Extractor Timing SNF Extractor - Compile Icon . ( Simulation 가 Stimulus 가

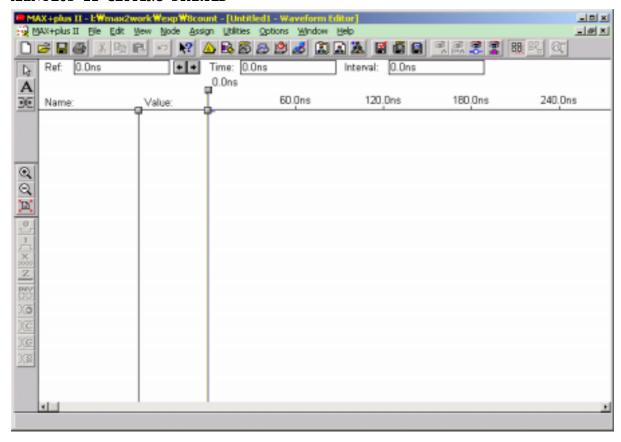

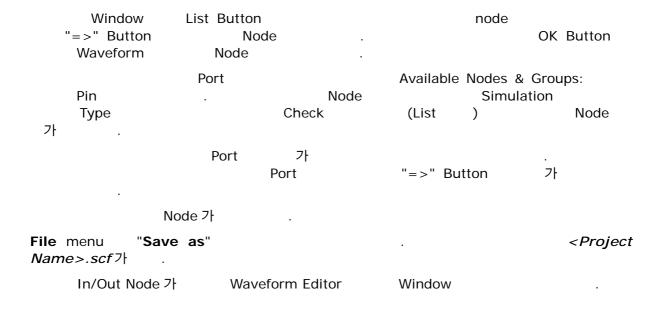

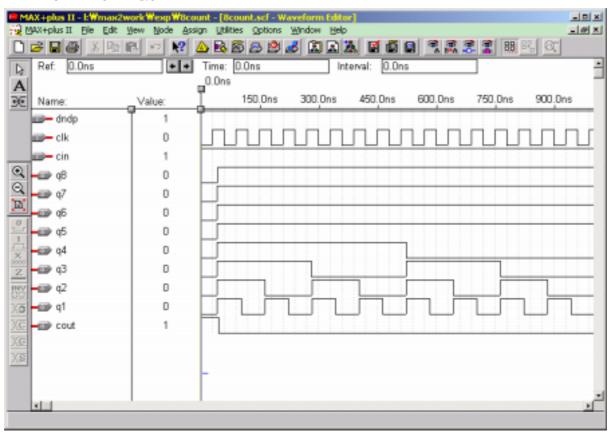

# Timing Simulation

32 Waveform

Editor 33 .

Figure 32 Waveform Editor 가

Figure 33 Waveform Editor

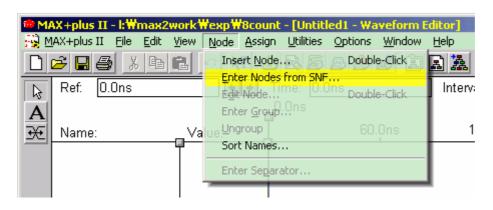

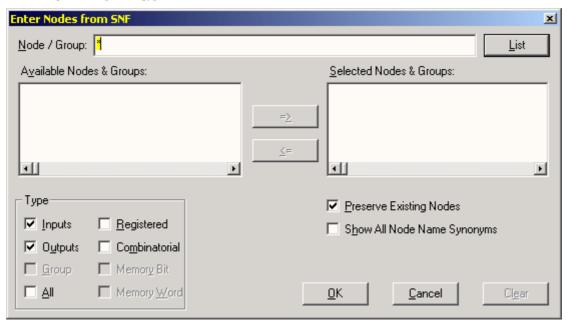

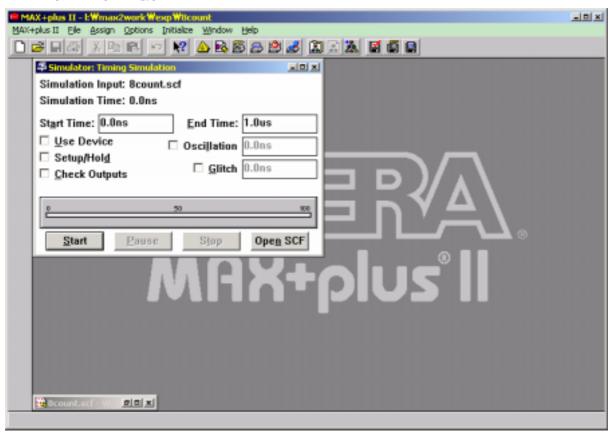

기 Node , Node -> Insert Node ; Node Name , Node -> Enter nodes from SNF ; SNF file Node . 35 Window 가 .

Figure 34 Node Enter Node From SNF...

Figure 35 Enter Node From SNF

Figure 36

| Icon            | Ioolar | Pin  |  |

|-----------------|--------|------|--|

| Stimulus Vector |        | Icon |  |

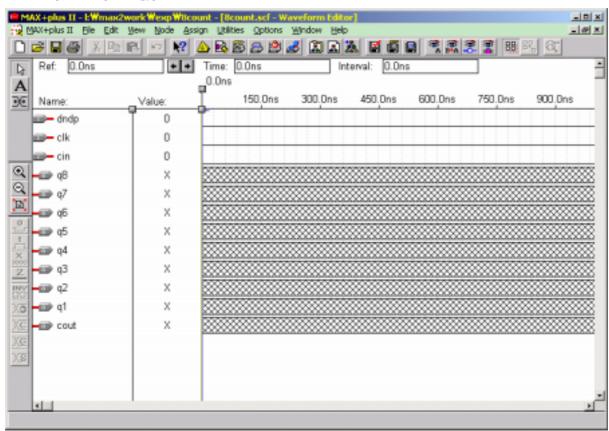

Grid Size... grid size 30ns , Option Waveform 37 Waveform Editor Stimulus Grid Grid 가 ½ Period 가 Block , Clock Grid MAX+plus II Option "Snap to Grid" .) "Snap to Grid" 가 Grid Clock Check

Figure 37 Stimulus

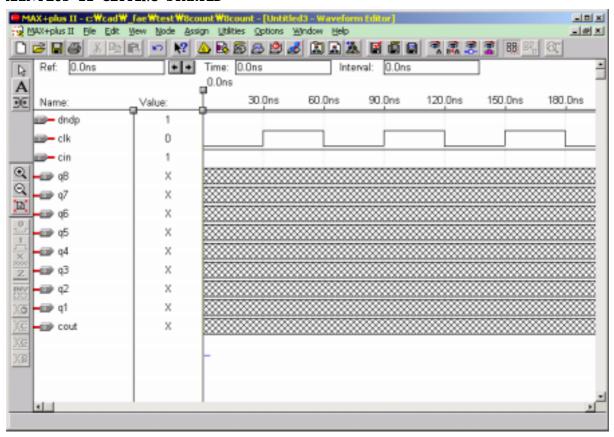

Waveform Editing 가 가 Simulation Waveform Simulation MAX+plus II S/W Main Menu MAX+plus II -> Simulator Simulation 38 Timing Simulation Waveform Simulation File Simulation Input: Waveform Start Time: End Time:

Figure 38 Simulator

| <b>Start</b> Button     | Simulator 가         | , Simulation | . Simulation |  |

|-------------------------|---------------------|--------------|--------------|--|

| Ope <u>n</u> SCF button | Simulation Waveform |              |              |  |

| 39 Simulation           |                     | . Timing     | Simulation   |  |

|                         | Target Device       | Delay        |              |  |

**Figure 39 Simulation**

MAX+plus II ....

Compile Hardware FPGA CPLD Configuration

Program 가 ....

가 ALTERA PLD S/W ...

## Revision History